# Low Power Design Using Adiabatic 2:1 MUX

# Smita Jagtap\* and Sandip Nemade

Technocrat Institute of Technology Excellence, Bhopal \*Corresponding author email id: smita.jagtap4u@gmail.com

Date of publication (dd/mm/yyyy): 31/01/2017

Abstract - A conventional CMOS logic circuit design approach depends upon charging the output capacitive nodes to the supply voltage or discharging it to the ground. This is one of the most used methods in VLSI designs. There are various techniques to design low power circuits both at system level as well as at circuit level to reduce power consumption. One of the major source of power dissipation is the charging and discharging of capacitor. Adiabatic circuits use the above two methods viz. slow charging of capacitor and discharging, and recycling of charge to minimize the power consumed. Several Adiabatic designs have been designed and tested in this paper. The technology used for simulation is 180 nm CMOS technology with 5v power supply. The input data rate for CMOS is made identical to that of adiabatic circuit. The comparison requires developing the circuit schematic based on both static CMOS and PFAL technique. Each circuit is simulated for different frequency and corresponding dynamic power is calculated through the tool Multisim V11.

Keywords - Adiabatic, CMOS, PFAL, ECRL.

#### I. Introduction

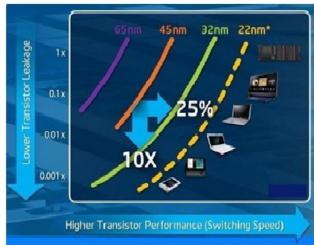

In the last few decades due to the ever growing demand for portable and small sized devices, integrated circuits require electronic circuit design methods to implement integrated circuits with low power consumption. The ever-growing number of transistors integrated on a chip and the increasing transistor switching speed in recent decades has enabled great performance improvement in computer systems by several orders of magnitude. Unfortunately, such phenomenal performance improvements have been accompanied by an increase in power and energy dissipation of the systems. If we want a design for low-power consumption to be successful, it is important to have a thorough understanding of the sources of power dissipation, the factors that affect them and the methodologies and techniques that are available to achieve optimal results. Therefore, this thesis starts with the sources of power dissipation in a integrated circuit. We present the most important low-power methodologies and power optimization techniques available. Low -power design can be applied on various different levels, such as the architectural level, the gate level, and the technology level. Apart from that, also a number of alternative logic-design styles are presented to report on their characteristics regarding power consumption. This section could as well be utilized by others as a quick study in the field of low-power/power-aware design. Passive losses due to leakage currents are in focus with on-going shrinking of microelectronic circuits. Powergating does not supply power to the inactive circuits from the power supply. Uncritical paths within a complex system can be equipped with higher devices, allowing for a trade- off of speed for passive losses. Apart from these circuit level methods to reduce leakage losses also new transistor models are presented to minimize leakage losses in circuits. Each of these revolutions has been a response to challenges posed by evolving semiconductor technology. The exponential increase in the chip density drove the adoption of language based design and synthesis, providing a dramatic increase in designer productivity. This approach held Moore's law at bay for a decade or so, but in the era of million gate designs, engineers discovered that there was a limit to how much new RTL could be written for new chip project. The result was the IP and design reuse became accepted as the only practical way to design large chips with relatively small design teams. Today even SoC design employs substantial IP in order to take advantage of the ever increasing density offered by submicron technology.

Moore's law

# II. METHODOLOGY

The three major sources of power dissipation in CMOS circuits is expressed using the equation given below:

SP Total = P Switching + P Short Circuit + P Leakage

P Total = VVDDFCLKCLoad + ISCVDD + ILeakageVDD

In equation above equations, the first term represents power dissipation due to transistor switching. V is the voltage swing,

Volume 6, Issue 1, ISSN: 2277 – 5668

CLoad is the load capacitance and F CLK is the switching frequency of the clock. The factor  $\alpha$  is the activity factor which represents the fraction of the circuit that is switching. In most cases the voltage swing for V is almost same as the supply voltage V<sup>DD</sup>, in such cases the term V is replaced with the second term in the equation represents short-circuits power dissipation which is the power dissipation in the CMOS when both PMOS and CMOS are ON simultaneously. When both transistors are ON a current value of ISC flows from the supply voltage to the ground and it is known as shortcircuit current ISC. Apart from these two terms viz. the switching power and short-circuit power, there is always present the power loss due to leakage currents. Leakage currents depend upon various fabrication technologies related factors like threshold voltage Vth, device dimensions, substrate injection etc. In previous years a major contribution to the power dissipation was due to the switching but we have managed it effectively by reducing the switching frequency. Now a days the main focus in on minimization of leakage loss in the circuits, a various numbers of circuit design techniques are proposed and we are going to discuss some of them.

Fig.2.1 Power Dissipation

# 2.1 The Charging Process in Adiabatic Logic Compared to Static CMOS

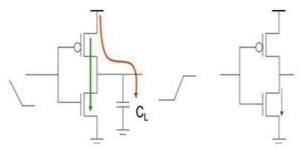

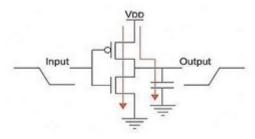

The energy dissipation due to switching of a simple CMOS inverter as shown in Fig.1 is observed. The capacitor C at the output of the gate is the input capacitance of the following gates. Whether the PMOS or NMOS will be ON is dependent upon the input signal. If the input voltage level changes from 1 to 0, energy is transferred from the voltage source to charge the output capacitor to the supply voltage  $V^{\rm DD}$ . A charge of Q=CVDD is taken from the voltage source, an energy quantum of E.

Fig. 3.2 Energy Dissipation

The energy dissipated in the circuit is equal to the

difference between the energy transferred from the sources and the energy stored in the circuit. Now if the input level changes from 0 to 1, in steady state condition the NMOS channel become ON and the PMOS is OFF. Charge stored on the output capacitance is then dissipated to the ground via the NMOS. The energy dissipation due to the switching of input level is given as

#### ECMOS= $1/2 \alpha \text{ CVDD}^2$

Where  $\alpha$  is the switching probability of the circuit, as there is no power loss in the circuit if no switching occurs in static CMOS (except leakage losses). Different approaches are used to reduce the energy dissipation in static CMOS. Number of transistor used for a certain operation can be reduced by following different algorithm, on structural and on circuit level. Voltage supply reduction is one of the easiest and most effective method to reduce power consumption, where as it slows the performance of the circuit. "In contrast to the above method Adiabatic Logic doesn't suddenly switches from 0 to t (and vice versa), but a voltage ramp is used to charge and recover the energy from the output of the circuit.

Fig. 2.3 ERCL

# 2.2 Energy Saving Factor

The energy saving factor (ESF) for a circuit can be defined as the ration between the energy dissipation by its static CMOS model and its adiabatic logic counterpart. It is a comparison of how much energy is dissipated by the static CMOS design as compared to adiabatic logic design. ESF compares the losses due to a single gate in the circuit. To calculate ESF we have to consider the supply voltage in static CMOS and power clock generation in adiabatic logic. The losses due to parasitic capacitance have also to be considered. A general definition of ESF is

# ESF= ECMOS/EALL

## 2.3 Low Power Design techniques

Different approaches are followed for a low power design whether It be circuit-based approach or an architectural approach, in higher level programming is used to optimize the power loss. In most of the cases a combination of these methods are used for circuit design. At the circuit level the major task is to minimize any one of the components. In the following paragraphs we have focused on different methods which are useful to minimize the losses in a design. We know that the energy required for a operation can be reduced by

decreasing the supply voltage. However due to constant threshold voltage and device capacitance the circuit performance will be slower.

# 2.4 An Adiabatic System

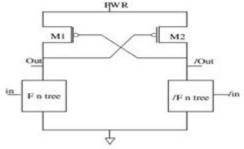

Two main parts of an adiabatic system are (i) Digital core design made up of adiabatic gates and the power-clock signal generator. We have used two adiabatic families in this paper. The most important aspect of the adiabatic system is clock-signal generation. High saving factors can be achieved by an optimal generation of four-phase power-clock. Positive Feedback Adiabatic Logic (PFAL) and the other is the Efficient Charge Recovery Logic (ECRL). Both operate in the same four-phase power-clock supply. PFAL is designed by the cross coupling of two inverters, which is the latch element.

Fig. 3.7 (Inverter circuits in PFAL (a) and ECRL Family

## III. RESULTS

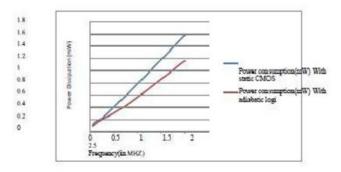

## 3.1 Power Comparison with Adiabatic and CMOS

by varying clock frequency

From above discussion, to compare the power dissipation with static CMOS and PFAL adiabatic logic the circuit simulation is performed using Multisim. The technology used for simulation is 180 nm CMOS technology with 5v power supply. The input data rate for CMOS 2:1 MUX is made identical to that of adiabatic circuit. The comparison requires developing the circuit schematic based on both static CMOS and PFAL technique. Each circuit is simulated for different frequency and corresponding dynamic power is calculated through the tool Multisim V11.

#### IV. CONCLUSION

The main idea of this project is to introduce the design of high performance and power efficient full adder design using multiplexer based pass transistor logic. In the current work, the full adder design is implemented by different logics like SERF, PFAL, and ECRL etc. Further the design is implemented using pass transistor logic combined with other logic. The number of transistors required for realizing mixed CMOS design of full adder is less than the number of transistors required in realizing the design of full adder using CMOS transistors independently. So, the required logic can be realized within an optimized area which performs faster when compared to the conventional static CMOS full adder design.

#### REFERENCES

- [1] Yazdi Ahmad, M. Micheal Green, "A 40-Gb/s Full-Rate 2:1 MUX in 0.18-µm CMOS" in proceeding of IEEE TRANSACTIONS ON Microwave Theory and Techniques, vol. 59, no. 11, November 2011..

- [2] Ahmed M. Shams, K. Tarek, A. Magdy, Bayoum, "Performance Analysis of Low-Power I-Bit CMOS Full Adder Cells", *IEEE transactions on very large scale integration (VLSI) systems*, vol. 10, no. 1, Feb. 2002.

- [3] Hing Mo Lam, Chi Ying Tsui, "A MUX-based High-Performance Single-Cycle CMOS Comparator", proceeding of IEEE TRANSACTIONS on Circuit and System, vol. 54, no. 7, July 2007.

- [4] W. Athas, L. Svensson, J.G. Koller, N. Tzartzanis, E.Y.-C. Chou, "Low-power digital systems based on adiabatic-switching principles", *IEEE Trans. on VLSI Systems*, vol. 2, no. 4, Dec. 1994.

- [5] Simran Kaur, Ashwini Kumar "Analysis of Low power SRAM cell using Tanner Tool" IJECT Vol. 3 Issue 1 Jan. -March 2012 ISSN 2230-9543

- [6] Y. Moon, D.K. Jeong, "An efficient charge recovery logic circuit", *IEEE Journal of Solid-State Circuits*, vol. 31, pp. 514-522, October 2014.

- [7] A. S. Sedra and K. C. Smith, Microelectronic Circuits, 4th ed, New York: Oxford, 1998.

- [8] G. Rama Tulasi, K. Venugopal, B. Vijayabaskar, R. SuryaPrakash, " Design &Analysis of full adders using adiabatic logic", International Journal of Engineering Research &Technology (IJERT), vol. 1, Issue 5. July 2012.

- [9] A. G. Dickinson and J. S. Denker, Adiabatic Dynamic Logic", Proceeding of the Custom Integrated Circuits Conference. IEEE (1994).

- [10] Jianping Hu, Lv Yu P-type Adiabatic Computing Based on Dual-Threshold CMOS and Gate-Length Biasing Techniques Journal of Convergence Information Technology(JCIT) Volume7, Number6, April 2012 issue 6.19

- [11] Byong-Deok Choi, Kyung Eun Kim, Ki-Seok Chung, and Dong Kyue Kim "Symmetric Adiabatic Logic Circuits against Differential Power Analysis " ETRI Journal, Volume 32, Number 1, February 2010

- [12] Charles L. Seitz, Alexander H. Frey, Sven Mattisson, Steve D. Rabin, Don A. Speck, and Jan L. A. van de Snepscheut, "Hot-clock nMOS," in Henry Fuchs, ed., 1985 Chapel Hill Conference on Very Large Scale Integration, pp. 1-17, Computer Science Press, 1985.